# Penguin Edge™ MVME8100 Series

Installation and Use P/N: 6806800P25P July 2022

#### **Legal Disclaimer\***

SMART Embedded Computing, Inc. (SMART EC), dba Penguin Solutions™, assumes no responsibility for errors or omissions in these materials. These materials are provided "AS IS" without warranty of any kind, either expressed or implied, including but not limited to, the implied warranties of merchantability, fitness for a particular purpose, or non-infringement. SMART EC further does not warrant the accuracy or completeness of the information, text, graphics, links, or other items contained within these materials. SMART EC shall not be liable for any special, indirect, incidental, or consequential damages, including without limitation, lost revenues or lost profits, which may result from the use of these materials. SMART EC may make changes to these materials, or to the products described therein, at any time without notice. SMART EC makes no commitment to update the information contained within these materials.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a SMART EC website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of SMART EC.

It is possible that this publication may contain reference to or information about SMART EC products, programming, or services that are not available in your country. Such references or information must not be construed to mean that SMART EC intends to announce such SMART EC products, programming, or services in your country.

#### Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by SMART EC.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

#### SMART Embedded Computing, Inc., dba Penguin Solutions

2900 S. Diablo Way, Suite 190 Tempe, Arizona 85282 USA

\*For full legal terms and conditions, visit https://www.penguinsolutions.com/edge/legal/

# **Table of Contents**

|                                         | 4- |

|-----------------------------------------|----|

| Safety Notes                            |    |

| Sicherheitshinweise                     | 21 |

| 1 Introduction                          |    |

| 1.1 Overview                            | 25 |

| 1.2 Feature Summary                     |    |

| 1.3 Ordering and Support Information    |    |

| 1.4 Standard Compliances                |    |

| 1.5 Mechanical Data                     |    |

| 2 Hardware Preparation and Installation |    |

| 2.1 Overview                            | 33 |

| 2.2 Unpacking and Inspecting the Board  |    |

| 2.3 Requirements                        |    |

|                                         |    |

| •                                       |    |

| 2.3.3 Thermal Requirements              |    |

| 2.3.4 Thermally Significant Components  |    |

| 2.3.5 Equipment Requirements            |    |

| 2.4 Configuring the Board               |    |

| 2.5 Installing Accessories              |    |

| 2.5.1 Rear Transition Module            |    |

|                                         |    |

|                                         |    |

| 2.6 Installing and Removing the Board   |    |

| 2.7 Completing the Installation         |    |

| 3 Connectors, LEDs, and Switches        |    |

| 3.1 Overview                            | 51 |

| 3.2 Front Panel                         |    |

| 3.3 Connectors                          |    |

## **Table of Contents**

|   |      | 3.3.1    | External Connectors               | <br> | <br>. 54 |

|---|------|----------|-----------------------------------|------|----------|

|   |      |          | 3.3.1.1 Front Panel Connectors    | <br> | <br>. 54 |

|   |      |          | 3.3.1.2 Backplane Connectors      | <br> | <br>. 55 |

|   |      | 3.3.2    | On-Board Connectors               | <br> | <br>. 61 |

|   | 3.4  | LEDS     |                                   | <br> | <br>. 71 |

|   |      | 3.4.1    | On-board LEDs                     | <br> | <br>. 72 |

|   | 3.5  | Switch   | es                                | <br> | <br>. 72 |

|   |      | 3.5.1    | Configuration Switches            | <br> | <br>. 73 |

|   |      |          | 3.5.1.1 S2 Switch                 | <br> | <br>. 73 |

|   |      |          | 3.5.1.2 S3 Switch                 | <br> | <br>. 74 |

|   |      |          | 3.5.1.3 S4 Switch                 | <br> | <br>. 76 |

|   |      |          | 3.5.1.4 S5 Switch                 | <br> | <br>. 76 |

|   |      |          | 3.5.1.5 Reset /Abort Switch       | <br> | <br>. 77 |

|   |      |          |                                   |      |          |

| 4 | Fund | tional I | Description                       | <br> | <br>. 79 |

|   |      |          | ·                                 |      |          |

|   | 4.1  |          | ew                                |      |          |

|   | 4.2  |          | Diagrams                          |      |          |

|   | 4.3  |          | ssor                              |      |          |

|   | 4.4  | -        | n Memory                          |      |          |

|   | 4.5  |          | D. 17. O                          |      |          |

|   |      |          | Real Time Clock                   |      |          |

|   |      |          | P5020/P5010 Internal Timers       |      |          |

|   |      |          | Watchdog Timers                   |      |          |

|   |      |          | 4.5.3.1 Initial Hardware Watchdog |      |          |

|   |      |          | 4.5.3.2 OS Watchdog               |      |          |

|   |      |          | CPLD Tick Timer                   |      |          |

|   | 4.6  |          | et Interfaces                     |      |          |

|   | 4.7  |          | erface                            |      |          |

|   |      |          | SPI Flash Memory                  |      |          |

|   |      |          | Firmware Redundancy               |      |          |

|   | 4.8  |          |                                   |      |          |

|   | 4.9  |          |                                   |      |          |

|   |      |          | ssor Console Port                 |      |          |

|   |      |          | JART Ports                        |      |          |

|   |      |          | Ports                             |      |          |

|   | _    | _        | Ports                             |      |          |

|   | 4.14 |          | (MC Sites                         |      |          |

|   |      | 4.14.1   | PMC Add-on Card                   | <br> | <br>. 89 |

|   |       | 4.14.2 XMC Add-on Card                    | 90 |

|---|-------|-------------------------------------------|----|

|   | 4.15  | SATA interface                            | 90 |

|   | 4.16  | VME Support                               | 90 |

|   |       | 4.16.1 Tsi148 VME Controller              | 90 |

|   |       | 4.16.2 Tsi384 PCle to PCI/PCI-X Bridge    | 90 |

|   | 4.17  | USB                                       | 91 |

|   | 4.18  | I2C Devices                               | 91 |

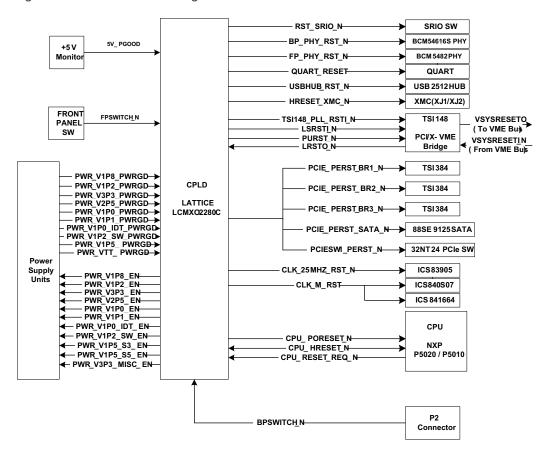

|   | 4.19  | Reset/Control CPLD                        | 92 |

|   | 4.20  | Power Management                          | 93 |

|   |       | 4.20.1 Power Distribution Structure       | 94 |

|   |       | 4.20.2 Power Sequence Requirements        | 94 |

|   | 4.21  | Clock Structure                           | 95 |

|   | 4.22  | Reset Structure                           | 96 |

|   | 4.23  | Interrupt Controller Assignments          | 97 |

|   | 4.24  | GPIO Electrical Characteristics           | 98 |

|   | 4.25  | Thermal Management                        | 98 |

|   |       |                                           |    |

| 5 | Boot  | System                                    | 01 |

|   |       |                                           |    |

|   | 5.1   | Overview                                  |    |

|   | 5.2   | Accessing U-Boot                          |    |

|   | 5.3   | Boot Options                              |    |

|   |       | 5.3.1 Booting from a Network              |    |

|   |       | 5.3.2 Booting from an Optional SATA Drive |    |

|   |       | 5.3.3 Booting from a USB Drive            |    |

|   |       | 5.3.4 Booting from eMMC                   |    |

|   |       | 5.3.5 Booting VxWorks through the Network |    |

|   | 5.4   | MVME8100 Series Specific U-Boot Commands  |    |

|   | 5.5   | Updating U-Boot                           | 80 |

|   |       |                                           |    |

| Α | Batte | ery Exchange                              | 09 |

|   | A 1   | Battery Exchange                          | 09 |

|   | ,     | Dation, Exchange                          | •  |

| В | Rela  | ted Documentation                         | 11 |

| _ |       |                                           |    |

|   | B.1   | Penguin Solutions Documentation           |    |

|   | B.2   | Related Specifications                    |    |

|   | B.3   | Manufacturers' Documents                  | 13 |

## **Table of Contents**

# **List of Figures**

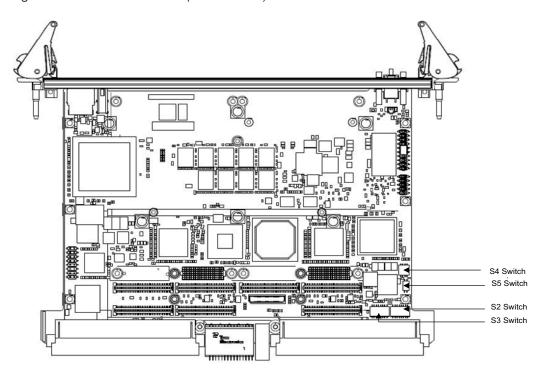

| Figure 2-1  | Switch Locations (ENP1 board)                         | 39  |

|-------------|-------------------------------------------------------|-----|

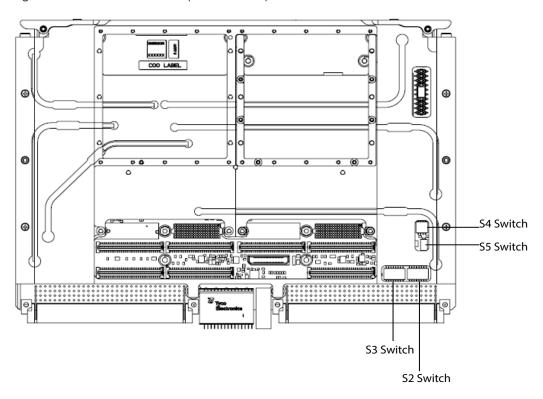

| Figure 2-2  | Switch Locations (ENP4 Board)                         | 40  |

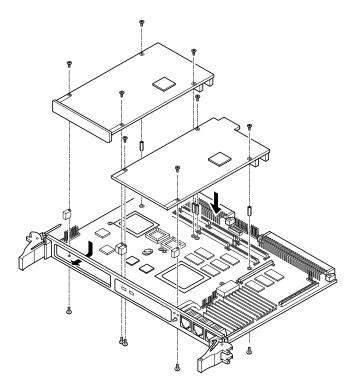

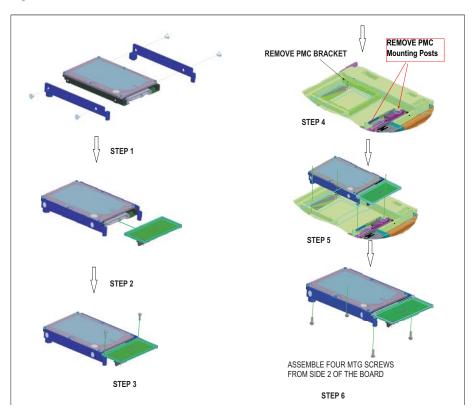

| Figure 2-3  | Typical Placement of a PMC/XMC Module on a VME Module | 44  |

| Figure 2-4  | SATA Drive Installation                               | 46  |

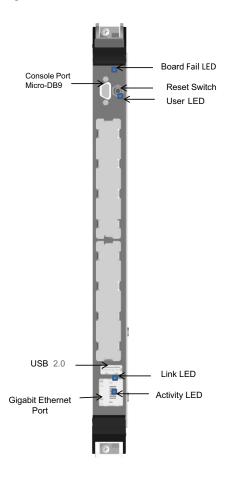

| Figure 3-1  | MVME8100 - ENP1 Board Connectors, LEDs, Switches      | 51  |

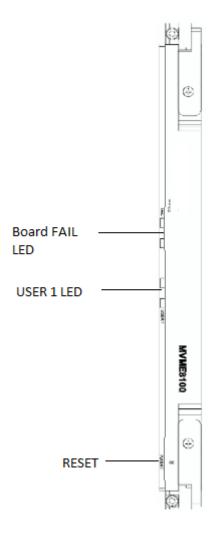

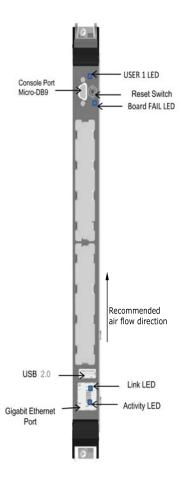

| Figure 3-2  | MVME8100 - ENP4 LEDs and Switches                     | 52  |

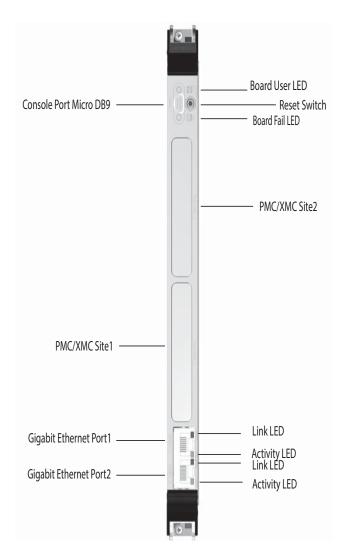

| Figure 3-3  | MVME8105 - ENP1 Board Connectors, LEDs, Switches      | 53  |

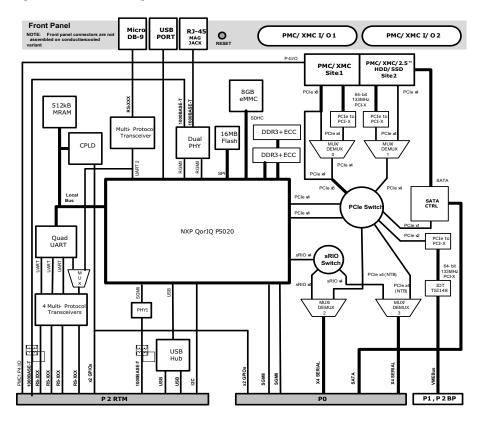

| Figure 4-1  | Block Diagram of MVME8100                             | 79  |

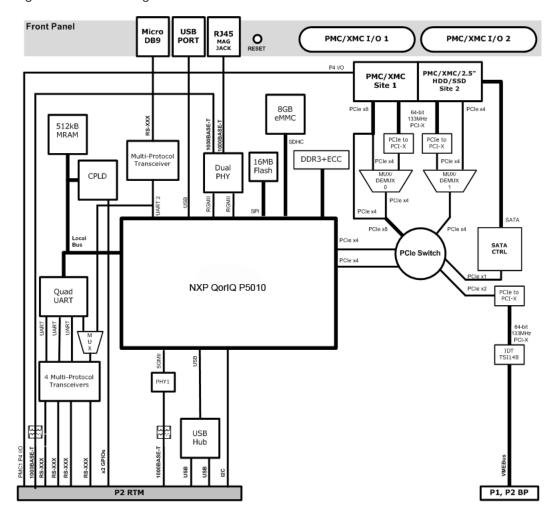

| Figure 4-2  | Block Diagram of MVME8105                             | 80  |

| Figure 4-3  | Block Diagram of MVME8110                             | 81  |

| Figure 4-4  | PCIe Ports                                            | 87  |

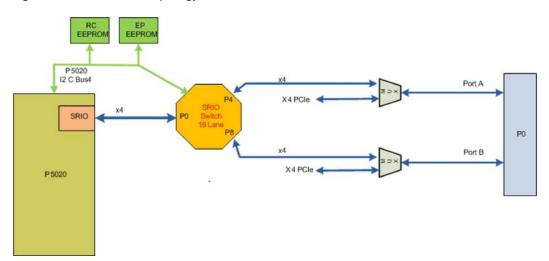

| Figure 4-5  | SRIO Bus Topology                                     | 88  |

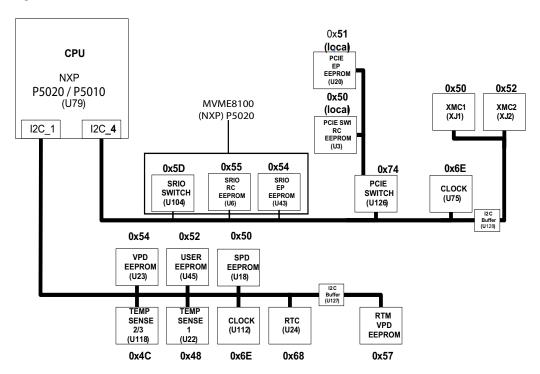

| Figure 4-6  | I2C Busses                                            | 92  |

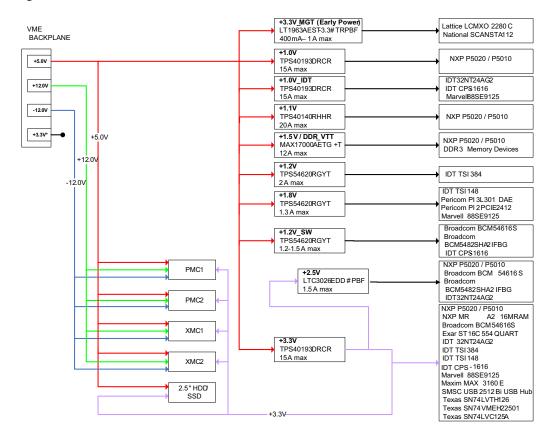

| Figure 4-7  | Power Distribution                                    | 94  |

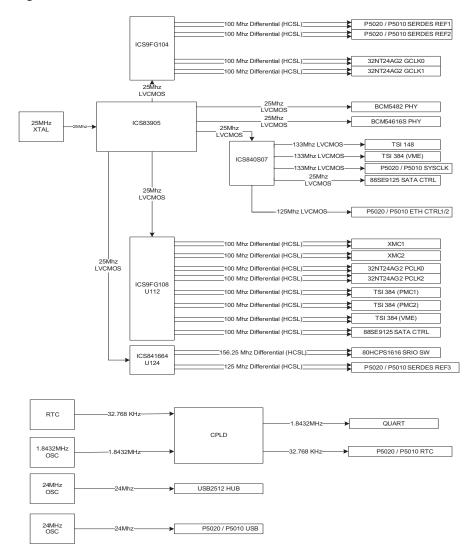

| Figure 4-8  | Clock Structure                                       | 95  |

| Figure 4-9  | Reset Control Diagram                                 | 96  |

| Figure 4-10 | Thermal Management                                    | 99  |

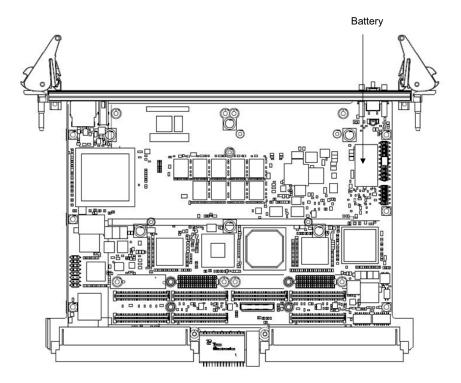

| Figure A-1  | Battery Location                                      | 109 |

## **List of Figures**

# **List of Tables**

| Table P1   | Conventions Table                              | 14    |

|------------|------------------------------------------------|-------|

| Table 1-1  | Board Feature Summary                          | 25    |

| Table 1-2  | Board Standard Compliances                     | 30    |

| Table 1-3  | Mechanical Data                                | 31    |

| Table 2-1  | MVME8100 Series Specifications                 | 35    |

| Table 2-2  | Operating Voltages                             | 37    |

| Table 2-3  | Power Requirements                             | 37    |

| Table 3-1  | Console Front Panel Connector (J1)             | 54    |

| Table 3-2  | Front Panel Tri-Speed Ethernet Connector (J4)  | 54    |

| Table 3-3  | USB Connector (J6)                             | 55    |

| Table 3-4  | P1 Connectors and Signal Descriptions          | 55    |

| Table 3-5  | P2 Connectors and Signal Descriptions          | 57    |

| Table 3-6  | VXS P0 Connector (applicable to MVME8100 only) | 60    |

| Table 3-7  | Customized SATA Connector (J3)                 | 62    |

| Table 3-8  | PMC J11/J21 Connector and Signal Description   | 63    |

| Table 3-9  | PMC J12/J22 Connector and Signal Descriptions  | 64    |

| Table 3-10 | PMC J13/J23 Connectors and Signal Descriptions | 66    |

| Table 3-11 | PMC J14 Connectors and Signal Descriptions     | 67    |

| Table 3-12 | Asset JTAG Header Pin Assignment (P12)         | 69    |

| Table 3-13 | XMC Connectors and Signal Descriptions         | 69    |

| Table 3-14 | Front Panel LEDs                               | 71    |

| Table 3-15 | On-board LEDs Status                           | 72    |

| Table 3-16 | S2 Switch Settings                             | 73    |

| Table 3-17 | S3 Switch Settings                             | 74    |

| Table 3-18 | Three Row Backplane Manual Slot Addressing     | 74    |

| Table 3-19 | S4 Switch Settings                             | 76    |

| Table 3-20 | S5 Switch Settings                             | 76    |

| Table 4-1  | P5020 / P5010 External Interrupt Assignments   | 97    |

| Table 4-2  | GPIO DC Electrical Characteristics             | 98    |

| Table 4-3  | GPIO Pull-Down Characteristics                 | 98    |

| Table 5-1  | MVME8100 SeriesSpecific U-Boot Commands        | . 105 |

| Table B-1  | Penguin Edge Documentation                     |       |

| Table B-2  | Related Specifications                         | . 111 |

| Table B-3  | Manufacturer's Publications                    | . 113 |

## **List of Tables**

## **About this Manual**

## **Overview of Contents**

This manual provides the information required to install and configure the Penguin Solutions MVME8100, MVME8105 and MVME8110 boards. Additionally, this manual provides specific preparation and installation information and data applicable to the board.

The MVME8100 and MVME8105 are high-performance, dual core processor boards featuring the NXP<sup>©</sup> QorlQ<sup>©</sup> P5020 processor.

The MVME8110 is a high-performance, single core processor board featuring the NXP QorlQ P5010 processor.

This manual contains the following sections, chapters and appendices:

Safety Notes on page 17 contains the cautions and warnings applicable to the use of this product.

Sicherheitshinweise on page 21 is a German translation of the Safety Notes chapter.

Chapter 1, Introduction on page 25 gives an overview of the features of the product, standard compliances, mechanical data, and ordering information.

Chapter 2, Hardware Preparation and Installation on page 33 outlines the installation requirements, hardware accessories, switch settings, and installation procedures.

Chapter 3, Connectors, LEDs, and Switches on page 51 describes external interfaces of the board. This includes connectors, LEDs, and switches.

Chapter 4, Functional Description on page 79 includes a block diagram and functional description of major components of the product.

Chapter 5, Boot System on page 101 describes the boot load software.

Appendix A, Battery Exchange on page 109 describes the procedure for replacing a battery.

Appendix B, Related Documentation on page 111 provides listings for publications, manufacturer's documents and related industry specification for this product.

# **Abbreviations**

This document uses the following abbreviations:

| TERM   | MEANING                                             |  |

|--------|-----------------------------------------------------|--|

| ANSI   | American National Standard Institute                |  |

| СМС    | Common Mezzanine Card                               |  |

| СОР    | Common On-chip Processor                            |  |

| CPLD   | Complex Programmable Logic Device                   |  |

| CRC    | Cyclic Redundancy Check                             |  |

| DDR    | Double Data Rate                                    |  |

| DIMM   | Dual In-line Memory Module                          |  |

| DMA    | Direct Memory Access                                |  |

| ECC    | Error Correction Code                               |  |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |  |

| eMMC   | Enhanced Module Management Controller               |  |

| FCC    | Federal Communications Commission                   |  |

| FIFO   | First In First Out                                  |  |

| GMII   | Gigabit Media Independent Interface                 |  |

| IEEE   | Institute of Electrical and Electronics Engineers   |  |

| I2C    | Inter IC                                            |  |

| IWD    | Initial Hardware Watchdog                           |  |

| JTAG   | Joint Test Access Group                             |  |

| LBC    | Local Bus Controller                                |  |

| MRAM   | Magnetoresistive random-access memory               |  |

| OSWD   | OS Watchdog                                         |  |

| PCIE   | Peripheral Component Interconnect Express           |  |

| PCI-X  | Peripheral Component Interconnect -X                |  |

| PIC    | Programmable Interrupt Controller                   |  |

| PIM    | PCI Mezzanine Card Input/Output Module              |  |

| TERM  | MEANING                                          |  |

|-------|--------------------------------------------------|--|

| PMC   | PCI Mezzanine Card                               |  |

| PLD   | Programmable Logic Device                        |  |

| PrPMC | Processor PCI Mezzanine Card                     |  |

| QUART | Quad Universal Asynchronous Receiver/Transmitter |  |

| RGMII | Reduced Gigabit Media Independent Interface      |  |

| RTC   | Real-Time Clock                                  |  |

| RTM   | Rear Transition Module                           |  |

| SATA  | Serial AT Attachment                             |  |

| SBC   | Single Board Computer                            |  |

| SDRAM | Synchronous Dynamic Random Access Memory         |  |

| SELV  | Safety Extra Low Voltage                         |  |

| SMT   | Surface Mount Technology                         |  |

| SGMII | Serial Gigabit Media Independent Interface       |  |

| SPD   | Serial Presence Detect                           |  |

| SRAM  | Static Random Access Memory                      |  |

| SRIO  | Serial Rapid IO                                  |  |

| TSEC  | Three-Speed Ethernet Controller                  |  |

| 2eSST | Two edge Source Synchronous Transfer             |  |

| UART  | Universal Asynchronous Receiver/Transmitter      |  |

| VITA  | VMEbus International Trade Association           |  |

| VME   | VMEbus (Versa Module Eurocard)                   |  |

| VPD   | Vital Product Data                               |  |

| XMC   | PCI Express Mezzanine Card                       |  |

# **Conventions**

The following table describes the conventions used throughout this manual.

Table P1 Conventions Table

| Notation       | Description                                                                                                   |  |

|----------------|---------------------------------------------------------------------------------------------------------------|--|

| 0x00000000     | Typical notation for hexadecimal numbers (digits are 0 through F), for example used for addresses and offsets |  |

| 0b0000         | Same for binary numbers (digits are 0 and 1)                                                                  |  |

| bold           | Used to emphasize a word                                                                                      |  |

| Screen         | Used for on-screen output and code related elements or commands.  Sample of Programming used in a table (9pt) |  |

| Courier + Bold | Used to characterize user input and to separate it from system output                                         |  |

| Reference      | Used for references and for table and figure descriptions                                                     |  |

| File > Exit    | Notation for selecting a submenu                                                                              |  |

| <text></text>  | Notation for variables and keys                                                                               |  |

| [text]         | Notation for software buttons to click on the screen and parameter description                                |  |

|                | Repeated item for example node 1, node 2,, node 12                                                            |  |

|                | Omission of information from example/command that is not necessary at the time                                |  |

|                | Ranges, for example: 04 means one of the integers 0,1,2,3, and 4 (used in registers)                          |  |

| I              | Logical OR                                                                                                    |  |

| A              | Indicates a hazardous situation which, if not avoided, could result in death or serious injury                |  |

| <u>.</u>       | Indicates a hazardous situation which, if not avoided, may result in minor or moderate injury                 |  |

Table P1 Conventions Table (continued)

| Notation                 | Description                                                                                        |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------|--|--|

| lack                     | Indicates a property damage message                                                                |  |  |

|                          | Indicates a hot surface that could result in moderate or serious injury                            |  |  |

| 4                        | Indicates an electrical situation that could result in moderate injury or death                    |  |  |

| Use ESD protection       | Indicates that when working in an ESD environment care should be taken to use proper ESD practices |  |  |

| Important<br>Information | No danger encountered, pay attention to important information                                      |  |  |

# **Summary of Changes**

This manual has been revised and replaces all prior editions.

| Part Number | Publication Date | Description                          |

|-------------|------------------|--------------------------------------|

| 6806800P25P | July 2022        | Rebrand to Penguin Solutions         |

| 6806800P25O | September 2018   | Rebrand to SMART Embedded Computing. |

## **About this Manual**

| Part Number | Publication Date | Description                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6806800P25N | April 2019       | Updated document template, minor grammar updates, converted list of product features to a comparison table. Changed Freescale to NXP in text and diagrams and figures where used. Removed Board Variants and Board Accessories tables; added references to product data sheets in the Related Documentation table (Appendix A). Updated Standard Compliances table. |

| 6806800P25M | July 2016        | Added a notice under Table 2-3 on page 45 and updated Table 1-1 on page 37.                                                                                                                                                                                                                                                                                         |

| 6806800P25L | May 2016         | Removed Declaration of Conformity of MVME8100,<br>Declaration of Conformity of MVME8105, and<br>Declaration of Conformity of MVME8110.                                                                                                                                                                                                                              |

| 6806800P25K | October 2015     | Changed as MVME8100/MVME8105/MVME8110.                                                                                                                                                                                                                                                                                                                              |

| 6806800P25J | July 2015        | Updated CPLD Tick Timer section.                                                                                                                                                                                                                                                                                                                                    |

| 6806800P25H | October 2014     | Updated Boot Options.                                                                                                                                                                                                                                                                                                                                               |

| 6806800P25G | September 2014   | Changed title as MVME8100 / MVME8110. Added information about MVME8110 and Declaration of Conformity.                                                                                                                                                                                                                                                               |

| 6806800P25F | June 2014        | Rebrand to Artesyn template.                                                                                                                                                                                                                                                                                                                                        |

| 6806800P25E | December 2013    | Added chapter Boot System.                                                                                                                                                                                                                                                                                                                                          |

| 6806800P25D | September 2013   | Updated Table 1-1, Table 1-2, Table 2-1, Table 2-3, PMC/XMC Installation, Table 3-2, and Table 3-5. Added Figure 2-2, SATA Installation, Figure 2-4, Figure 3-2, Interrupt Controller Assignments and GPIO Electrical Characteristics.                                                                                                                              |

| 6806800P25C | December 2012    | Updated Standard Compliances.                                                                                                                                                                                                                                                                                                                                       |

| 6806800P25B | November 2012    | GA release.                                                                                                                                                                                                                                                                                                                                                         |

| 6806800P25A | May 2012         | First edition.                                                                                                                                                                                                                                                                                                                                                      |

# **Safety Notes**

This section provides warnings that precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed during all phases of operation, service, and repair of this equipment. You should also employ all other safety precautions necessary for the operation of the equipment in your operating environment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

Penguin Solutions™ intends to provide all necessary information to install and handle the product in this manual. Because of the complexity of this product and its various uses, we do not guarantee that the given information is complete. If you need additional information, ask your Penguin Solutions representative.

This product is a Safety Extra Low Voltage (SELV) device designed to meet the EN60950-1 requirements for Information Technology Equipment. The use of the product in any other application may require safety evaluation specific to that application.

Only personnel trained by Penguin Solutions or persons qualified in electronics or electrical engineering are authorized to install, remove or maintain the product.

The information given in this manual is meant to complete the knowledge of a specialist and must not be used as replacement for qualified personnel.

Keep away from live circuits inside the equipment. Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment.

Do not install substitute parts or perform any unauthorized modification of the equipment or the warranty may be voided. Contact your local Penguin Solutions representative for service and repair to make sure that all safety features are maintained.

### **EMC**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications.

Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense. Changes or modifications not expressly approved by Penguin Solutions could void the user's authority to operate the equipment. Board products are tested in a representative

system to show compliance with the above mentioned requirements. A proper installation in a compliant system will maintain the required performance. Use only shielded cables when connecting peripherals to assure that appropriate radio frequency emissions compliance is maintained.

Warning! This is a Class A device. This device may cause radio interference in residential areas. In this case, the operator may be required to take appropriate measures.

## **Operation**

#### **Product Damage**

High humidity and condensation on the board surface causes short circuits.

Do not operate the board outside the specified environmental limits.

Make sure the board is completely dry and there is no moisture on any surface before applying power.

#### **Damage of Circuits**

Electrostatic discharge and incorrect installation and removal can damage circuits or shorten their life.

Before touching the board or electronic components, make sure that you are working in an ESD-safe environment.

#### **Board Malfunction**

Switches marked as reserved might carry production-related functions and can cause the board to malfunction if their setting is changed.

Do not change settings of switches marked as reserved. The setting of switches which are not marked as reserved has to be checked and changed before board installation.

## Installation

#### **Data Loss**

Powering down or removing a board before the operating system or other software running on the board has been properly shut down may cause corruption of data or file systems.

Make sure all software is completely shut down before removing power from the board or removing the board from the chassis.

#### **Product Damage**

Only use injector handles for board insertion to avoid damage to the front panel and/or PCB. Deformation of the front panel can cause an electrical short or other board malfunction.

#### **Product Damage**

Inserting or removing modules with power applied may result in damage to module components.

Before installing or removing additional devices or modules, read the documentation that came with the product.

## **Cabling and Connectors**

#### **Product Damage**

RJ-45 connectors on modules are either twisted-pair Ethernet (TPE) or E1/T1/J1 network interfaces. Connecting an E1/T1/J1 line to an Ethernet connector may damage your system.

- Make sure that TPE connectors near your working area are clearly marked as network connectors.

- Verify that the length of an electric cable connected to a TPE bushing does not exceed 100 meters.

- Make sure the TPE bushing of the system is connected only to safety extra low voltage circuits (SELV circuits).

If in doubt, ask your system administrator.

## **Battery**

#### **Board/System Damage**

Incorrect exchange of lithium batteries can result in a hazardous explosion.

When exchanging the on-board lithium battery, make sure that the new and the old battery are exactly the same battery models. If the respective battery model is not available, contact your local Penguin Solutions sales representative for the availability of alternative, officially approved battery models.

#### **Data Loss**

Exchanging the battery can result in loss of time settings. Backup power prevents the loss of data during exchange.

Quickly replacing the battery may save time settings.

#### **Data Loss**

If the battery has low or insufficient power the RTC is initialized.

Exchange the battery before seven years of actual battery use have elapsed.

#### **PCB** and Battery Holder Damage

Removing the battery with a screw driver may damage the PCB or the battery holder. To prevent damage, do not use a screw driver to remove the battery from its holder.

### **Environment**

Improper disposal of used products may harm the environment. Always dispose of used products according to your country's legislation and manufacturer's instructions.

## Sicherheitshinweise

Dieses Kapitel enthält Hinweise, die potentiell gefährlichen Prozeduren innerhalb dieses Handbuchs vorrangestellt sind. Beachten Sie unbedingt in allen Phasen des Betriebs, der Wartung und der Reparatur des Systems die Anweisungen, die diesen Hinweisen enthalten sind. Sie sollten außerdem alle anderen Vorsichtsmaßnahmen treffen, die für den Betrieb des Produktes innerhalb Ihrer Betriebsumgebung notwendig sind. Wenn Sie diese Vorsichtsmaßnahmen oder Sicherheitshinweise, die an anderer Stelle diese Handbuchs enthalten sind, nicht beachten, kann das Verletzungen oder Schäden am Produkt zur Folge haben.

Penguin Solutions™ ist darauf bedacht, alle notwendigen Informationen zum Einbau und zum Umgang mit dem Produkt in diesem Handbuch bereit zu stellen. Da es sich jedoch um ein komplexes Produkt mit vielfältigen Einsatzmöglichkeiten handelt, können wir die Vollständigkeit der im Handbuch enthaltenen Informationen nicht garantieren. Falls Sie weitere Informationen benötigen sollten, wenden Sie sich bitte an die für Sie zuständige Geschäftsstelle von Penguin Solutions.

Das Produkt wurde entwickelt, um die Sicherheitsanforderungen für SELV Geräte nach der Norm EN 60950-1 für informationstechnische Einrichtungen zu erfüllen. Die Verwendung des Produkts in einer anderen Anwendung erfordert eine Sicherheitsüberprüfung für diese spezifische Anwendung.

Einbau, Wartung und Betrieb dürfen nur von durch Penguin Solutions ausgebildetem oder im Bereich Elektronik oder Elektrotechnik qualifiziertem Personal durchgeführt werden. Die in diesem Handbuch enthaltenen Informationen dienen ausschließlich dazu, das Wissen von Fachpersonal zu ergänzen, können dieses jedoch nicht ersetzen.

Halten Sie sich von stromführenden Leitungen innerhalb des Produktes fern. Entfernen Sie auf keinen Fall Abdeckungen am Produkt. Nur werksseitig zugelassenes Wartungspersonal oder anderweitig qualifiziertes Wartungspersonal darf Abdeckungen entfernen, um Komponenten zu ersetzen oder andere Anpassungen vorzunehmen.

Installieren Sie keine Ersatzteile oder führen Sie keine unerlaubten Veränderungen am Produkt durch, sonst verfällt die Garantie. Wenden Sie sich für Wartung oder Reparatur bitte an die für Sie zuständige Geschäftsstelle von Penguin Solutions. So stellen Sie sicher, dass alle sicherheitsrelevanten Aspekte beachtet werden.

### **EMV**

Das Produkt wurde in einem Penguin Edge™ Standardsystem getestet. Es erfüllt die für digitale Geräte der Klasse A gültigen Grenzwerte in einem solchen System gemäß den FCC-Richtlinien Abschnitt 15 bzw. EN 55022 Klasse A. Diese Grenzwerte sollen einen angemessenen Schutz vor Störstrahlung beim Betrieb des Produktes in Gewerbe- sowie Industriegebieten gewährleisten.

Das Produkt arbeitet im Hochfrequenzbereich und erzeugt Störstrahlung. Bei unsachgemäßem Einbau und anderem als in diesem Handbuch beschriebenen Betrieb können Störungen im Hochfrequenzbereich auftreten.

Wird das Produkt in einem Wohngebiet betrieben, so kann dies mit grosser Wahrscheinlichkeit zu starken Störungen führen, welche dann auf Kosten des Produktanwenders beseitigt werden müssen. Änderungen oder Modifikationen am Produkt, welche ohne ausdrückliche Genehmigung von Penguin Solutions durchgeführt werden, können dazu führen, dass der Anwender die Genehmigung zum Betrieb des Produktes verliert. Boardprodukte werden in einem repräsentativen System getestet, um zu zeigen, dass das Board den oben aufgeführten EMV-Richtlinien entspricht. Eine ordnungsgemässe Installation in einem System, welches die EMV-Richtlinien erfüllt, stellt sicher, dass das Produkt gemäss den EMV-Richtlinien betrieben wird. Verwenden Sie nur abgeschirmte Kabel zum Anschluss von Zusatzmodulen. So ist sichergestellt, dass sich die Aussendung von Hochfrequenzstrahlung im Rahmen der erlaubten Grenzwerte bewegt.

Warnung! Dies ist eine Einrichtung der Klasse A. Diese Einrichtung kann im Wohnbereich Funkstörungen verursachen. In diesem Fall kann vom Betreiber verlangt werden, angemessene Maßnahmen durchzuführen.

#### **Betrieb**

#### Beschädigung des Produktes

Hohe Luftfeuchtigkeit und Kondensat auf der Oberfläche des Produktes können zu Kurzschlüssen führen.

Betreiben Sie das Produkt nur innerhalb der angegebenen Grenzwerte für die relative Luftfeuchtigkeit und Temperatur. Stellen Sie vor dem Einschalten des Stroms sicher, dass sich auf dem Produkt kein Kondensat befindet.

### Beschädigung von Schaltkreisen

Elektrostatische Entladung und unsachgemäßer Ein- und Ausbau des Produktes kann Schaltkreise beschädigen oder ihre Lebensdauer verkürzen.

Bevor Sie das Produkt oder elektronische Komponenten berühren, vergewissern Sie sich, daß Sie in einem ESD-geschützten Bereich arbeiten.

#### Fehlfunktion des Produktes

Schalter, die mit Reserved gekennzeichnet sind, können mit produktionsrelevanten Funktionen belegt sein. Das Ändern dieser Schalter kann im normalen Betrieb Störungen auslösen.

Verstellen Sie nur solche Schalter, die nicht mit Reserved gekennzeichnet sind. Prüfen und ggf. ändern Sie die Einstellungen der nicht mit Reserved gekennzeichneten Schalter, bevor Sie das Produkt installieren.

### Installation

#### **Datenverlust**

Das Herunterfahren oder die Deinstallation eines Boards bevor das Betriebssystem oder andere auf dem Board laufende Software ordnungsmemäss beendet wurde, kann zu partiellem Datenverlust sowie zu Schäden am Filesystem führen.

Stellen Sie sicher, dass sämtliche Software auf dem Board ordnungsgemäss beendet wurde, bevor Sie das Board herunterfahren oder das Board aus dem Chassis entfernen.

#### Beschädigung des Produktes

Fehlerhafte Installation des Produktes kann zu einer Beschädigung des Produktes führen.

Verwenden Sie die Handles, um das Produkt zu installieren/deinstallieren. Auf diese Weise vermeiden Sie, dass das Face Plate oder die Platine deformiert oder zerstört wird.

#### Beschädigung des Produktes und von Zusatzmodulen

Fehlerhafte Installation von Zusatzmodulen, kann zur Beschädigung des Produktes und der Zusatzmodule führen

Lesen Sie daher vor der Installation von Zusatzmodulen die zugehörige Dokumentation.

### Kabel und Stecker

#### Beschädigung des Produktes

Bei den RJ-45-Steckern, die sich an dem Produkt befinden, handelt es sich entweder um Twisted-Pair-Ethernet (TPE) oder um E1/T1/J1-Stecker. Beachten Sie, dass ein versehentliches Anschließen einer E1/T1/J1-Leitung an einen TPE-Stecker das Produkt zerstören kann.

- Kennzeichnen Sie deshalb TPE-Anschlüsse in der Nähe Ihres Arbeitsplatzes deutlich als Netzwerkanschlüsse.

- Stellen Sie sicher, dass die L\u00e4nge eines mit Ihrem Produkt verbundenen TPE-Kabels 100 m nicht \u00fcberschreitet.

- Das Produkt darf über die TPE-Stecker nur mit einem Sicherheits-Kleinspannungs-Stromkreis (SELV) verbunden werden.

Bei Fragen wenden Sie sich an Ihren Systemverwalter.

#### **Batterie**

#### Beschädigung des Blades

Ein unsachgemäßer Einbau der Batterie kann gefährliche Explosionen und Beschädigungen des Blades zur Folge haben.

Verwenden Sie deshalb nur den Batterietyp, der auch bereits eingesetzt wurde undbefolgen Sie die Installationsanleitung.

#### **Datenverlust**

Wenn Sie die Batterie austauschen, können die Zeiteinstellungen verloren gehen. Eine Backupversorgung verhindert den Datenverlust während des Austauschs.

Wenn Sie die Batterie schnell austauschen, bleiben die Zeiteinstellungen möglicherweise erhalten.

#### **Datenverlust**

Wenn die Batterie wenig oder unzureichend mit Spannung versorgt wird, wird der RTC initialisiert.

Tauschen Sie die Batterie aus, bevor sieben Jahre tatsächlicher Nutzung vergangen sind.

#### Schäden an der Platine oder dem Batteriehalter

Wenn Sie die Batterie mit einem Schraubendreher entfernen, können die Platine oder der Batteriehalter beschädigt werden.

Um Schäden zu vermeiden, sollten Sie keinen Schraubendreher zum Ausbau der Batterie verwenden.

## **Umweltschutz**

Unsachgemäße Entsorgung von gebrauchten Produkten kann die Umwelt schädigen. Entsorgen Sie gebrauchte Produkte stets gemäß der in Ihrem Land gültigen Gesetzgebung und den Empfehlungen des Herstellers.

## Introduction

## 1.1 Overview

The MVME8100 single board computer is a VMEbus board based on the NXP<sup>®</sup> QorlQ<sup>®</sup> P5020 processor. It is a high performance 6U VME/VXS board targeted towards high-end military and industrial automation applications using VMEbus technology. The MVME8100 is compliant with the VMEbus International Trade Association (VITA) standards VMEbus, 2eSST, and PCI-X. The MVME8100 can accommodate two PCI/PCI Express Mezzanine Cards (PMC/XMC).

The MVME8105 is a dual core non-VXS version of the MVME8100 board based on the NXP QorlQ P5020 processor. It runs at 2.0GHz with 4GB DDR3. The MVME8105 provides a second 1000Base-TX RJ-45 interface on the front panel.

The MVME8110 is a single core non-VXS version of the MVME8100 board based on the NXP QorIQ P5010 processor. It runs at 1.2GHz with 2GB DDR3.

## 1.2 Feature Summary

The following table provides a summary of features for all three board variations. Not all processor features are implemented on the board.

| Table 1-1 | Board Feature Summary |

|-----------|-----------------------|

|-----------|-----------------------|

| Feature                                          | MVME<br>8100        | MVME<br>8105      | MVME<br>8110      |

|--------------------------------------------------|---------------------|-------------------|-------------------|

| NXP <sup>®</sup> QorlQ <sup>®</sup> Processor    | P5020<br>(1.8/2GHz) | P5020<br>(2.0GHz) | P5010<br>(1.2GHz) |

| e5500 cores                                      | 2                   | 2                 | 1                 |

| 10GbE (XAIU) controllers                         | 1                   | 1                 | 1                 |

| 1GbE controllers (SGMII and RGMII)               | 5                   | 5                 | 5                 |

| 64-bit DDR3/3L SDRAM memory controllers with ECC | 2                   | 2                 | 1                 |

| Programmable Interrupt Controller (PIC)          | Υ                   | Υ                 | Υ                 |

| I <sup>2</sup> C controllers                     | 4                   | 4                 | 4                 |

| 2-pin/4-pin UARTs                                | 4/2                 | 4/2               | 4/2               |

| 4-channel DMA engines                            | 2                   | 2                 | 2                 |

| Enhanced local bus controller                    | 1                   | 1                 | 1                 |

## Introduction

Table 1-1 Board Feature Summary (continued)

| Feature                                                                   | MVME<br>8100 | MVME<br>8105 | MVME<br>8110 |

|---------------------------------------------------------------------------|--------------|--------------|--------------|

| PCI Express 2.0 controller/ports                                          | 4            | 4            | 4            |

| Serial Rapid IO controller/ports v1.3 compliant with features of v2.1)    | 2            | 2            | 2            |

| Enhanced secure digital host controller (SD/MMC)                          | 1            | 1            | 1            |

| Enhanced Serial Peripheral Interfaces (eSPI with four chip selects)       | 1            | 1            | 1            |

| High-speed USB 2.0 controllers with integrated PHYs                       | 2            | 2            | 2            |

| CoreNet platform cache with ECC                                           | 2Mbyte       | 2Mbyte       | 1Mbyte       |

| SATA 2.0 controller                                                       | 2            | 2            | 2            |

| RAID5/6 engine                                                            | 1            | 1            | 1            |

| SEC encryption                                                            | Υ            | N            | N            |

| System Memory                                                             |              |              |              |

| DDR3 SDRAM with ECC                                                       | 4GB          | 4GB          | 2GB          |

| DDR3 data rate                                                            | 1333MT/s     | 1333MT/s     | 1200MT/s     |

| SMBus                                                                     |              |              |              |

| 512Kbit user configuration serial EEPROM                                  | Y            | Y            | Y            |

| 256B serial presence detect (SPD) EEPROMs                                 | Y            | Y            | Y            |

| 64Kbit Vital Product Data (VPD) EEPROM                                    | Υ            | Y            | Y            |

| Real Time Clock (RTC) with battery backup**                               | Υ            | Y            | Y            |

| Temperature sensors                                                       | Y            | Y            | Y            |

| RTM and XMC VPD EEPROMs                                                   | Υ            | Y            | Y            |

| Flash                                                                     |              |              |              |

| Soldered SPI Flash, 8MB each, switchable for uboot primary/backup support | 2            | 2            | 2            |

Table 1-1 Board Feature Summary (continued)

| Feature                                                                  | MVME<br>8100 | MVME<br>8105 | MVME<br>8110 |

|--------------------------------------------------------------------------|--------------|--------------|--------------|

| Hardware switch or software bit write protection for entire logical bank | Y            | Y            | Y            |

| eMMC Flash                                                               | 8GB          | 8GB          | 8GB          |

| NVRAM                                                                    |              | •            |              |

| Magneto resistive Random Access Memory (MRAM)                            | 512KB        | 512KB        | 512KB        |

| PCI Express                                                              |              |              |              |

| 4x ports to VXS backplane P0 (muxed with SRIO ports)                     | 2            | -            | -            |

| 8x port to PMC/XMC Site 1                                                | 1            | 1            | 1            |

| 4x port to PMC/XMC Site 2                                                | 1            | 1            | 1            |

| SRIO - 4x ports to VXS backplane P0 (muxed with PCIe ports)              | 2            | -            | -            |

| USB                                                                      |              |              |              |

| USB 2.0 for front panel I/O                                              | 1            | -            | 1            |

| USB 2.0 for backplane RTM I/O                                            | 2            | 2            | 2            |

| Ethernet                                                                 |              |              |              |

| 10/100/1000BASE-T Ethernet port to front panel                           | 1*           | 2            | 1            |

| 10/100/1000BASE-T Ethernet channels to P2/RTM                            | 2            | 1            | 2            |

| 1000BASE-BX Ethernet SERDES channels to P0 backplane/RTM                 | 2            | -            | -            |

| SATA Ports                                                               | '            | <u>'</u>     |              |

| SATA Gen 3 ports to P0 backplane/RTM                                     | 2            | -            | -            |

| Serial Ports                                                             |              | 1            |              |

| RS-232/422/485 console port to front panel or P2/RTM                     | 1            | 1            | 1            |

| RS-232/422/485 COM ports to P2/RTM                                       | Up to 4      | Up to 4      | Up to 4      |

Table 1-1 Board Feature Summary (continued)

| Feature                                                                           | MVME<br>8100 | MVME<br>8105 | MVME<br>8110 |

|-----------------------------------------------------------------------------------|--------------|--------------|--------------|

| VMEbus - VME64x and 2eSST                                                         | Υ            | Υ            | Υ            |

| Timers                                                                            | •            |              |              |

| 32-bit timers in CPU                                                              | 8            | 8            | 8            |

| Watchdog timer in CPU                                                             | Y            | Y            | Y            |

| PMC/XMC sites with 64-bit PMCIO on Site 1                                         | 2            | 2            | 2            |

| Option for 2.5" SATA SSD (PMC/XMC Site 2)                                         | Υ            | Y            | Y            |

| GPIO Interface to RTM/P0                                                          | 4            | 2            | 2            |

| VXS Interface                                                                     | •            |              |              |

| VITA 41 specification compliant                                                   | Υ            | Y            | Y            |

| Supports backplane P0 connector                                                   | Υ            | -            | -            |

| Form Factor                                                                       | •            |              |              |

| Standard 6U, one slot                                                             | Υ            | Y            | Y            |

| Support 0.8 and 0.85 inch slot chassis                                            | Υ            | Y            | Y            |

| Support heat frame on both sides for conduction cooled board                      | Υ            | Y            | Y            |

| Software Support                                                                  |              |              |              |

| VxWorks                                                                           | Υ            | Y            | Y            |

| Linux                                                                             | Υ            | Y            | Y            |

| Compatible with RTM (assembly # 0106852M***)                                      | Υ            | Y            | Y            |

| I/O                                                                               | 1            |              |              |

| Micro DB-9 connector for console port on front panel                              | 1*           | 1            | 1            |

| USB 2.0 Type A connector on front panel                                           | 1*           | -            | 1            |

| Front panel RJ-45 connector with integrated LEDs for 10/100/1000 Ethernet channel | 1*           | 2            | 1            |

Table 1-1 Board Feature Summary (continued)

| Feature                                                                                    | MVME<br>8100 | MVME<br>8105 | MVME<br>8110 |

|--------------------------------------------------------------------------------------------|--------------|--------------|--------------|

| PMC/XMC Site 1 front I/O and rear PMC I/O                                                  | Υ            | Υ            | Υ            |

| PMC/XMC Site 2 front I/O                                                                   | Υ            | Y            | Y            |

| Serial ports to P2/RTM, (two Micro DB-9 connectors on RTM panel and two on planar headers) | 4            | 4            | 4            |

| 10/100/1000BASE-T Ethernet channels to RJ-45 connectors on RTM panel                       | 2            | 1            | 2            |

| 1000BASE-BX Ethernet SERDES channels to backplane                                          | 2            | -            | -            |

| USB 2.0 ports to RTM with USB Type A connectors on RTM panel                               | 2            | 2            | 2            |

| SATA port to RTM with eSATA connector on RTM                                               | 2            | -            | -            |

| GPIOs to planar headers on RTM (See note below)                                            | 4            | 2            | 2            |

| Other Features                                                                             |              |              |              |

| Front panel RESET switch                                                                   | Υ            | Y            | Y            |

| LED front panel status indicators (four user/fail/ready LEDs)                              | Y            | Y            | Y            |

| Planar status indicators                                                                   | Υ            | Y            | Y            |

| Boundary scan support                                                                      | Υ            | Y            | Υ            |

<sup>\*</sup>Not present in ENP4 version

**NOTE:** The front panel I/O connectors are available only in ENP1 (air cooled variants). I/O signals in the ENP4 (conduction cooled) variant are accessed through P2 only.

<sup>\*\*</sup>Battery not present in ENP4 version

# 1.3 Ordering and Support Information

Refer to the data sheets for the MVME81xx series of boards for a complete list of available variants and accessories. Refer to Appendix B or consult your local Penguin Solutions sales representative for the availability of other variants.

For technical assistance, documentation, or to report product damage or shortages, contact your local Penguin Solutions sales representative or visit <a href="https://www.penguinsolutions.com/edge/support//">https://www.penguinsolutions.com/edge/support//</a>

## 1.4 Standard Compliances

The MVME8100 Series is designed to be CE compliant and to meet the following standard requirements.

Table 1-2 Board Standard Compliances

| Standard                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UL 60950-1<br>EN 60950-1<br>IEC 60950-1<br>CAN/CSA C22.2 No 60950-1              | Safety Requirements (legal)                                                                                                                                                                                                                                                                                                                                                        |

| CISPR 22<br>EN 55022<br>EN 55024<br>FCC Class A<br>VCCI Japan<br>AS/NZS CISPR 22 | EMC requirements (legal) on system level (predefined Penguin Solutions system)                                                                                                                                                                                                                                                                                                     |

| ETSI EN 300 019 series                                                           | Environmental Requirements                                                                                                                                                                                                                                                                                                                                                         |

| Directive (EU) 2015/863<br>(amending Annex II to<br>Directive 2011/65/EU)        | Directive on the restriction of the use of certain hazardous substances in electrical and electronic equipment (RoHS).  The MVME8100-202180404 ENP4 version is not RoHS compliant. It was compliant with RoHS 5 of 6 until the exemption expired in 2016. Customers may still purchase the non-RoHS product (with a waiver) for use in applications excluded from RoHS compliance. |

# 1.5 Mechanical Data

The MVME8100 is a full 6U board with added mounting holes to support an ENP4 board variant. The MVME8100 Series occupies a single VME card slot.

The following table provides detailed mechanical data information.

Table 1-3 Mechanical Data

| Characteristic           | Value                          |

|--------------------------|--------------------------------|

| Height                   | 233.44mm (9.2 inches)          |

| Depth                    | 160.0mm (6.3 inches)           |

| Front Panel Height       | 261.8mm (10.3 inches)          |

| Width                    | 19.8mm (0.8 inches)            |

| Maximum Component Height | 14.8mm (0.58 inches)           |

| Weight (estimated)       | 0.58Kg (ENP1)<br>0.90Kg (ENP4) |

## Introduction

# **Hardware Preparation and Installation**

## 2.1 Overview

This chapter provides startup and safety instructions related to this product, hardware preparation instruction that includes default switch settings. System considerations and installation instructions for the baseboard, PMC, XMC, and Rear Transition Module (RTM) are also described in this chapter.

A fully implemented MVME8100 board consists of the baseboard plus:

- Two single-wide or one double-wide PCI Mezzanine Card (PMC) slot for added versatility.

- One rear transition module for support of the mapped I/O from the Product Name Short baseboard to the P2 connector.

NOTE: RTM is not applicable to the ENP4 version.

Up to two optional XMC cards (in place of PMC modules).

Following are the steps to be performed before using the board. Be sure to read the entire chapter, including all caution and warning notes, before you begin.

- 1. Unpack the hardware. Unpacking and Inspecting the Board on page 34.

- 2. Configure the hardware by setting jumpers on the board and RTM. *Configuring the Board on page 38*.

- 3. Install the MVME8100 RTM (VXS1-RTM1) or the MVME8110 RTM (MVME8110-RTM) in the chassis. *Rear Transition Module on page 41*.

- 4. Install PMC module (if required). *Installing Accessories on page 41*.

- 5. Install XMC module (if required). *Installing Accessories on page 41*.

- 6. Install the MVME8100 board in the chassis. *Installing and Removing the Board on page* 47.

- 7. Attach cabling and apply power. Completing the Installation on page 48.

- 8. Install PIM on transition module (if required). Refer to the *VXS1-RTM1and MVME8110-RTM Installation and Use* manual.

- 9. Examine and/or change environmental parameters. *MVME8100 Series Single Board Computer Programmer's Reference*.

- 10. Program the board as needed for your applications. *MVME8100 Series Single Board Computer Programmer's Reference*.

# 2.2 Unpacking and Inspecting the Board

Read all notices and cautions prior to unpacking the product.

Use ESD protection

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or shorten their life.

Before touching the board or electronic components, make sure that you are working in an ESD-safe environment.

#### **Shipment Inspection**

To inspect the shipment, perform the following steps:

- 1. Verify that you have received all items of your shipment:

- MVME8100 board

- Quick Start Guide

- Safety Notes Summary

- Any optional items ordered

- 2. Check for damage and report any damage or differences to customer service.

- 3. Remove the desiccant bag shipped together with the board and dispose of it according to your country's legislation.

The product is thoroughly inspected before shipment. If any damage occurred during transportation or any items are missing, contact customer service immediately.

## 2.3 Requirements

Make sure that the board, when operated in your particular system configuration, meets the requirements specified in the next sections.

## 2.3.1 Environmental Requirements

The following table lists the currently available specifications for the environmental characteristics of the MVME8100. A complete functional description of the MVME8100 baseboard appears in Chapter 4.

The MVME8100 has ENP1 and ENP4 variants which comply with the following environmental and regulatory specifications.

The MVME8105 has ENP1variant only which comply with the following environmental and regulatory specifications.

The MVME8110 has ENP1variant only which comply with the following environmental and regulatory specifications.

For ENP1 boards, the operating temperatures refer to the temperature of the air circulating around the board and not to the component temperature.

For ENP4 board, the operating temperature refers to the temperature at the card edge frame.

Table 2-1 MVME8100 Series Specifications

| Characteristics       | ENP1         | ENP4           |

|-----------------------|--------------|----------------|

| Cooling Method        | Forced Air   | Conduction     |

| Operating temperature | 0°C to +55°C | -40°C to +85°C |

## **Hardware Preparation and Installation**

Table 2-1 MVME8100 Series Specifications (continued)

| Characteristics                | ENP1                                                              | ENP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Temperature            | -40° C to +85° C                                                  | -55°C to +105°C  Note: The MVME8100 ENP 4 version includes NAND Flash memory in the form of the eMMC. The specified storage limits for the MVME8100 ENP 4 version are -55°C to +105°C. It should be noted that the industry standard (for Flash) as well as the specific vendor of this component only warrants performance (without data degradation) from -40°C to +85°C. Storage of the MVME8100 outside this range (while supported by other components on the board) may result in an unspecified reduction in the data retention capabilities of the eMMC. |

| Relative humidity              | To 95% RH                                                         | To 100% RH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vibration Sine (10min/axis)    | 2G, 5 to 500Hz                                                    | 10G, 15 to 2000Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Vibration Random<br>(1hr/axis) | 0.002g <sup>2</sup> /Hz, 15 to<br>2000Hz <sup>1</sup><br>(2G RMS) | 0.1g <sup>2</sup> /Hz, 15 to 2000Hz (12GRMS) <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Shock                          | 20g/11mS                                                          | 40g/11mS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conformal Coating              | No                                                                | Option (Acrylic)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### **Product Damage**

High humidity and condensation on the board surface causes short circuits.

Do not operate the board outside the specified environmental limits.

Make sure the board is completely dry and there is no moisture on any surface before applying power.

## 2.3.2 Power Requirements

The MVME8100 Series uses the backplane +5V source to power each on board power supply. The +3.3V backplane supply is not utilized in order to have backward compatibility with old 3-row chassis. The -12V and +12V is routed through to the XMC and PMC connectors. The power estimates provided in the following table is the total board consumption from +5V, excluding the PMC/XMC, SATA HDD/SSD and USB devices.

Table 2-2 Operating Voltages

| Voltages | Minimum        | Normal | Maximum     |

|----------|----------------|--------|-------------|

| +5.0V    | 4.875V (-2.5%) | 5.0V   | 5.25V (+5%) |

Table 2-3 Power Requirements

| Board Variant                  | Power                                                         |

|--------------------------------|---------------------------------------------------------------|

| MVME8100-202200401S/E          | Board idle at OS prompt: 38 Watts, typical                    |

| MVME8105-01E<br>MVME8110-01S/E | Operating load*: 42 Watts, typical 54 Watts, Max(@55°C)       |

| (ENP1)                         | *Operating conditions: No RTM, PMC/XMC or peripherals.        |

| MVME8100-202180404<br>(ENP4)   | Operating load*: 65 Watts, max (@ 85°C card edge temperature) |

The MVME8100-202180404 is non-compliant with the EU RoHS Directive and the CE mark as of July 21, 2016.

The following table shows the power limits due to the available 5 volts pins, when the MVME8100/MVME8105 is installed in either a 3-row or 5-row chassis and when PMCs/XMCs are present.

| Chassis Type | Power Limit | Power limits PMCs or XMCs |  |  |

|--------------|-------------|---------------------------|--|--|

| 3-Row        | 70W maximum | Below 70W <sup>1</sup>    |  |  |

| 5-Row        | 90W maximum | Below 90W <sup>1</sup>    |  |  |

<sup>1.</sup> Keep below power limit. Cooling limitations must be considered.

## 2.3.3 Thermal Requirements

The MVME8100 Series boards requires a minimum air flow of 10CFM uniformly distributed across the board, with the airflow traveling in the direction from PMC/XMC 1 to PMC/XMC 2, when operating at a 55°C (131°F) ambient temperature.

## 2.3.4 Thermally Significant Components

The chassis into which the MVME8100 Series boards are installed must provide sufficient airflow to maintain proper board operating temperature. The P5020/P5010 processor temperature should be monitored while the board is operational to ensure that the processor core temperature does not exceed 100°C. The processor core temperature can be read using the I²C sensor at address 0x4C on the processor I²C bus #1. For more information, refer MVME8100/MVME8105/MVME8110 Single Board Computer Programmer's Reference.

## 2.3.5 Equipment Requirements

The following equipment is recommended to complete a system using an MVME8100, MVME8105 or MVME8110 board:

- VMEbus system enclosure

- System console terminal

- Operating system (and/or application software)

# 2.4 Configuring the Board

The board provides software control over most options. Settings can be modified to fit the user's specifications. To configure, set the bits in the control register after installing the board in a system. Make sure that all user-defined switches are properly set before installing a PMC/XMC module. For more information about switches, see *Switches on page* 72.

Prior to installing PMC modules on the baseboard, ensure that all switches that are user configurable are set properly. Refer to *Figure 2-1* or the board itself, for the location of specific switches and set the switches according to the descriptions provided in *Configuration Switches on page 73*.

Figure 2-1 Switch Locations (ENP1 board)

Figure 2-2 Switch Locations (ENP4 Board)

# 2.5 Installing Accessories

This section describes the procedures for installing the RTM, PMCs, and the XMCspan on the baseboard.

### 2.5.1 Rear Transition Module

The RTM of MVME8100 Series does not support hot swap. You must remove power to the system before installing the module. Before installing the transition module, you may need to manually configure the RTM switches and install a PMC I/O Module (PIM).

Use ESD protection

#### **Damage of Circuits**

Electrostatic discharge and incorrect installation and removal can damage circuits or shorten their life.

Before touching the board or electronic components, make sure that you are working in an ESD-safe environment.

#### **Product Damage**

Only use injector handles for board insertion to avoid damage to the front panel and/or PCB. Deformation of the front panel can cause an electrical short or other board malfunction.

#### **Board Malfunction**

Switches marked as reserved might carry production-related functions and can cause the board to malfunction if their setting is changed.

Do not change settings of switches marked as reserved. The setting of switches which are not marked as reserved has to be checked and changed before board installation.

#### **Installation Procedure**

To begin the installation of the RTM in a chassis, proceed as follows:

- Turn all equipment power OFF and disconnect the power cable from the AC power source.

- 2. Remove the chassis cover as instructed in the equipment user's manual.